Design of 8 nibble RAM (Memory) using Behavior Modeling Style -

|

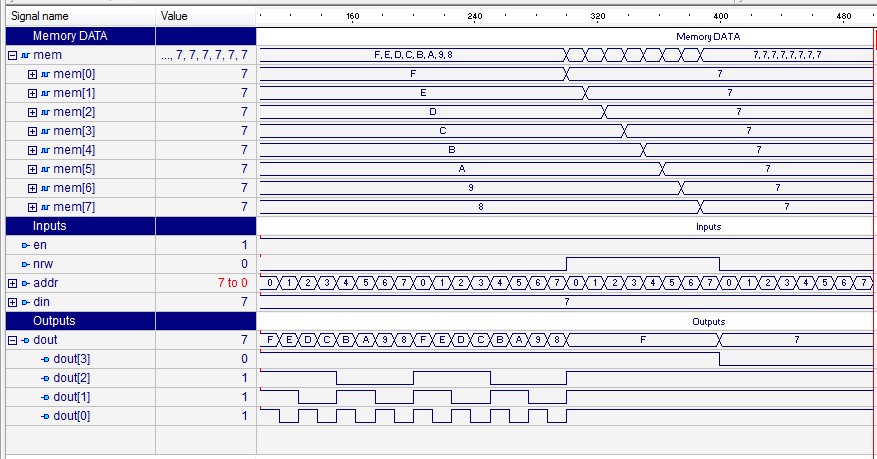

| Output Waveform : 8 Nibble RAM (Memory) |

VHDL Code -

-------------------------------------------------------------------------------

--

-- Title : RAM

-- Design : vhdl_upload2

-- Author : Naresh Singh Dobal

-- Company : nsdobal@gmail.com

-- VHDL Programs & Exercise with Naresh Singh Dobal.

--

--

-------------------------------------------------------------------------------

--

-- File : Design of RAM (8 nibble) using behavior modeling style.vhd

library IEEE;

use IEEE.STD_LOGIC_1164.all;

use ieee.std_logic_arith.all;

use ieee.std_logic_unsigned.all;

entity RAM is

port(

en : in STD_LOGIC;

nrw : in STD_LOGIC;

addr : in STD_LOGIC_VECTOR(2 downto 0);

din : in STD_LOGIC_VECTOR(3 downto 0);

dout : out STD_LOGIC_VECTOR(3 downto 0)

);

end RAM;

architecture RAM_arc of RAM is

type memory is array (0 to 7) of std_logic_vector (3 downto 0);

signal mem : memory := (0=>"1111",

1 => "1110",

2 => "1101",

3 => "1100",

4 => "1011",

5 => "1010",

6 => "1001",

7 => "1000");

begin

memory_design : process (en,addr,nrw,din) is

begin

if (en='1') then

if (nrw='0') then

dout <= mem(conv_integer (addr));

else

mem (conv_integer (addr)) <= din;

end if;

end if;

end process memory_design;

end RAM_arc;

No comments:

Post a Comment